Dunque, faccio un piccolo aggiornamento alla questione.

Non sono riuscito a far ripartire la mia macchina virtuale contenente Windows. Si lamenta che c'è un file hal.dll che manca e non parte del tutto. Non dovrebbe essere un problema rinfrescare il sistema, se non ché non so dove più ho messo la mia copia di Win XP... Quando salterà fuori, vedrò di ripristinare il sistema.

Ricordiamo prima di tutto il problema iniziale, che è quello di amplificare di 30dB un segnale proveniente da una matrice di elettrodi disposti su dei neuroni. E' presente un elettrodo di riferimento ed il circuito va fabbricato in una sessantina di esemplari, il che richiede di mantenerne bassa la complessità. La banda richiesta è quella telefonica, da 300Hz a 3kHz e sarebbe preferibile cercare di ridurre il più possibile il disturbo a 50Hz proveniente dalla rete elettrica. Non è dato sapere l'impedenza di un neurone, ma penso che sia utile fare in modo che il circuito abbia un ingresso che carichi il meno possibile l'elettrodo.

Non volevo però rimanere del tutto a bocca asciutta dopo aver proposto una possibile soluzione, e quindi ho rispolverato una versione di Spice 3f5 che avevo installato sul MacOSX. Si tratta della versione distribuita da Berkeley, che ha dato origine alle varie personalizzazioni che si trovano nei vari software (LTspice, Altium designer, ...). Non la uso proprio tutti i giorni, ma l'impressione generale che ne ho ricavato in questi ultimi anni è che si possono fare tante cose, ma rispetto alle versioni commerciali ogni tanto c'è qualche problema di convergenza, perlomeno nella simulazione transitorio.

Mentre programmi come LTspice permettono di introdurre un circuito in forma grafica, Spice richiede una descrizione in formato testo, che in gergo si chiama una netlist. Anche utilizzando i programmi con editor grafici, conviene sempre avere un'idea di come funzioni il formato delle netlist, perché la maggior parte di essi se ne serve per comunicare con la propria versione adattata di Spice.

Si tratta di un formato molto semplice, in pratica si danno dei nomi ai vari nodi del circuito e poi si provvede a disporre i vari compontenti dicendo fra quali nodi vanno posti. Iniziamo quindi a fornire il circuito, con evidenziati i nodi, è lo stesso che avevo fornito qualche tempo fa, ma ho ritoccato il valore di qualche componente. I nomi dei nodi sono i numeretti disegnati in rosso nello schema.

Per simulare gli operazionali, si può procedere a cercare un modello nella biblioteca di qualche fabbricante, oppure si può cercare di costruirselo da sé, andando a leggersi la sterminata letteratura che esiste in merito.

Io ho spesso utilizzato i modelli presi da questa pagina:

http://www.ecircuitcenter.com/opmodels/OpampModels.htmUna lettura molto interessante è anche questa application note:

http://www.analog.com/static/imported-f ... 6AN138.pdfPossiamo partire da un operazionale di tipo TL082. E' abbastanza veloce, non è troppo critico, è facilissimo da reperire ed è economico. Non cerchiamo operazionali di precisione per applicazioni in cui la precisione non serve, non cerchiamo bande passanti fantasmagoriche per poi ritrovarci amplificatori che autooscillano mettendo all'uscita un cavo coassiale (cosa che peraltro può benissimo succedere anche al TL082).

Leggendo un po' di datasheet e modificando il modello di livello 3 della pagina web che ho citato, sono arrivato a questo:

- Codice: Seleziona tutto

* OPAMP MACRO MODEL (INTERMEDIATE LEVEL)

* WITH OUTPUT VOLTAGE LIMITING

* IN+ IN- OUT VCC VEE

.SUBCKT OPAMP3 1 2 81 101 102

Q1 5 1 7 NPN

Q2 6 2 8 NPN

RC1 101 5 5.17e2

RC2 101 6 5.17e2

RE1 7 4 4.66e2

RE2 8 4 4.66e2

I1 4 102 0.001

*

* OPEN-LOOP GAIN, FIRST POLE AND SLEW RATE

G1 100 10 6 5 0.0104719

RP1 10 100 1.03e8

CP1 10 100 7.76e-5uF

*

* CURRENT LIMIT

D1 10 82 DILIM

VL1 82 81 DC 0.186V

D2 83 10 DILIM

VL2 81 83 DC 0.186V

.model DILIM D(IS=1E-15)

*

*OUTPUT STAGE

EOUT 80 100 10 100 1

RO 80 81 100

*

* INTERNAL REFERENCE

RREF1 101 103 100K

RREF2 103 102 100K

EREF 100 0 103 0 1

R100 100 0 1MEG

*

.model NPN NPN(BF=50000)

*

.ENDS

Non che non sia criticabile, il TL082 utilizza un ingresso a JFET mentre nel modello si continua ad utilizzare dei bipolari per rappresentare lo stadio di ingresso. In particolare, ho cercato di rappresentare la limitazione in corrente dello stadio di uscita.

Un'altra possibilità la troviamo sul sito di Texas Instruments, dove è scaricabile gratuitamente un modello che loro forniscono per il TL082, però utilizza alcune estensioni che non sono compatibili con la mia versione di Spice.

Si può certamente fare di meglio, ma io non passerei troppo tempo a simulare un circuito del genere: si accende il saldatore e lo si monta!

Ecco quindi la netlist completa. Ci sono due modelli di operazionale, uno è quello di cui ho parlato sopra, l'altro invece è una rappresentazione piuttosto semplicistica, tant'è che neppure richiede alimentazione!

- Codice: Seleziona tutto

* Circuito acquisizione segnali biologici banda 300Hz-3kHz con filtro notch 50Hz

Vin 3 0 DC 0V AC 1mV

Vcc 1 0 DC 15V

Vee 2 0 DC -15V

C1 3 4 68pF

L1 4 5 3nH

C2 5 0 0.5pF

R1 5 0 10Megohm

* X1 5 6 7 OPAMP1

X1 5 6 7 1 2 OPAMP3

R2 6 0 4.7kohm

R3 6 7 150kohm

C3 6 7 180pF

R4 7 8 96.46kohm

C7 8 0 66nF

R5 8 10 96.46kohm

C5 7 9 33nF

C6 9 10 33nF

R6 9 0 48.22k

* X2 10 11 12 OPAMP1

X2 10 11 12 1 2 OPAMP3

R8 11 0 4.7kohm

R7 11 12 150kohm

C8 11 12 470pF

.TRAN

.AC DEC 100 1 1MEG

.PRINT AC V(3)

.PRINT AC V(5)

.PRINT AC V(7)

.PRINT AC V(10)

.PRINT AC V(12)

* SINGLE-POLE OPERATIONAL AMPLIFIER MACRO-MODEL

* connections: non-inverting input

* | inverting input

* | | output

* | | |

.SUBCKT OPAMP1 1 2 6

* INPUT IMPEDANCE

RIN 1 2 10MEG

* DC GAIN (100K) AND POLE 1 (100HZ)

EP1 3 0 1 2 100K

RP1 3 4 1K

CP1 4 0 1.5915uF

* OUTPUT BUFFER AND RESISTANCE

EOUT 5 0 4 0 1

ROUT 5 6 10

.ENDS

* OPAMP MACRO MODEL (INTERMEDIATE LEVEL)

* WITH OUTPUT VOLTAGE LIMITING

* IN+ IN- OUT VCC VEE

.SUBCKT OPAMP3 1 2 81 101 102

Q1 5 1 7 NPN

Q2 6 2 8 NPN

RC1 101 5 5.17e2

RC2 101 6 5.17e2

RE1 7 4 4.66e2

RE2 8 4 4.66e2

I1 4 102 0.001

*

* OPEN-LOOP GAIN, FIRST POLE AND SLEW RATE

G1 100 10 6 5 0.0104719

RP1 10 100 1.03e8

CP1 10 100 7.76e-5uF

*

* CURRENT LIMIT

D1 10 82 DILIM

VL1 82 81 DC 0.186V

D2 83 10 DILIM

VL2 81 83 DC 0.186V

.model DILIM D(IS=1E-15)

*

*OUTPUT STAGE

EOUT 80 100 10 100 1

RO 80 81 100

*

* INTERNAL REFERENCE

RREF1 101 103 100K

RREF2 103 102 100K

EREF 100 0 103 0 1

R100 100 0 1MEG

*

.model NPN NPN(BF=50000)

*

.ENDS

Facciamo una prima analisi del circuito. Mi sono interessato in particolare all'analisi AC, che viene fatta calcolando il punto di lavoro del circuito, linearizzando i componenti attorno al punto di lavoro e poi risolvendo il circuito linearizzato nel dominio della frequenza. Si tratta quindi di una simulazione che non può dare conto di effetti di saturazione o non lineari e che quindi non è adatta a studiare cose tipo la distorsione armonica, mentre è perfetta per determinare la banda passante di un circuito quando tutto funziona bene.

Ho introdotto dapprima i valori mostrati nel circuito sopra per vedere se avevo fatto i calcoli corretti, in particolare per essere sicuro che il filtro notch filtrasse effettivamente a 50 Hz.

Ho in un secondo tempo rifatto i conti utilizzando valori di resistenze standard all'1%, per essere sicuro che questa soluzione fosse effettivamente praticabile. Per i condensatori, quello da 66nF si potrà realizzare con un parallelo tra due condensatori di 33nF:

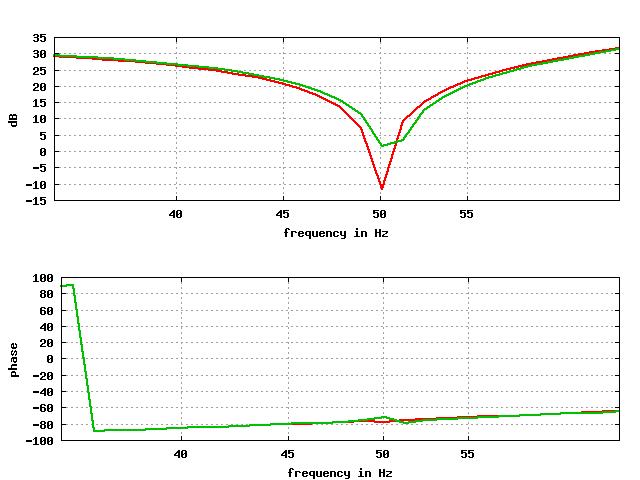

La figura qui di seguito mostra, in rosso, la simulazione effettuata con il filtro notch originale ed in verde, con il filtro realizzato con valori standard:

- Risultati analisi AC

- analysis.png (6.95 KiB) Osservato 3491 volte

Si vede come il fatto di aver rotto leggermente la simmetria del circuito faccia sì che il filtro notch intervenga su una frequenza leggermente diversa ed abbia un pozzo meno "profondo" di quello con i componenti più ideali. Non credo che la cosa sia un problema nell'utilizzazione pratica, perché l'attenuazione resta più che buona a 50 Hz:

- Risultati analisi AC, zoom attorno a 50 Hz

- analysis_prec.png (5.22 KiB) Osservato 3491 volte

Tra l'altro, la profondità del filtro con i valori "teorici" non è infinita, perché ho riportato i valori con quattro cifre significative.

Ma non è il caso di spaccare il capello in quattro.

Naturalmente, il discorso non è finito qui, si potrebbero far variare le caratteristiche degli operazionali, si potrebbe fare uno studio Monte Carlo sui componenti per vedere che tolleranza è necessaria, si potrebbe vedere cosa succede con un'analisi di tipo transitorio e apprezzare la distorsione armonica... Ma io a questo punto lo monterei, il circuitino

Volendo utilizzare due operazionali in più, potrei studiare un filtro anti aliasing più efficiente di quel poco che ho messo qui (due poli e due zeri messi a naso).

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)

, dovresti vedere che il polo introdotto dal condensatore C1 si sposta verso il basso, e così fa lo zero introdotto da C2 che si abbassa pure. Magari in un'applicazione realistica si può alzare un po' C2, ma non troppo.

, dovresti vedere che il polo introdotto dal condensatore C1 si sposta verso il basso, e così fa lo zero introdotto da C2 che si abbassa pure. Magari in un'applicazione realistica si può alzare un po' C2, ma non troppo.

instead of

instead of  (Anonimo).

(Anonimo). ain't

ain't  , right?

, right? in lieu of

in lieu of  .

. for

for  arithm.

arithm.