Buongiorno mi sono appena iscritta... devo sostenere un esame all'univeristà e avrei bisogno del vostro aiuto...

Vi posto il mio problema trammite una foto allegata che rende tutto più chiaro...

spero che qualcuno possa aiutarmi!!

Grazie in anticipo

problema con circuito flip-flop

Moderatori: ![]() carloc,

carloc, ![]() g.schgor,

g.schgor, ![]() BrunoValente,

BrunoValente, ![]() IsidoroKZ

IsidoroKZ

16 messaggi

• Pagina 1 di 2 • 1, 2

1

voti

Ciao, innanzitutto dalla prossima volta scrivi direttamente il testo senza allegare le immagini così diventa tutto più fluido. Per gli schemi usa FidoCad (di cui trovi una guida qui: http://www.electroyou.it/darwinne/wiki/fidocadj).

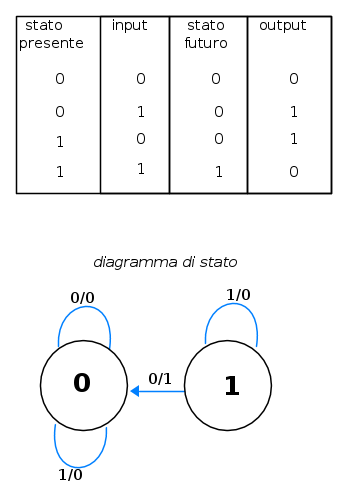

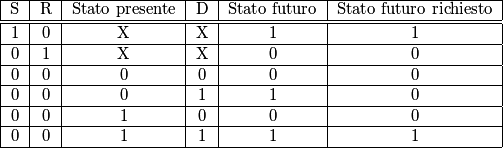

Il diagramma degli stati comunque non mi torna, in particolare dallo stato 0 con ingresso 1 l'output dovrebbe essere 1, non zero. Che ci sia un errore lo vedi anche contando il numero di uscite pari a 1: nella consegna sono previsti due 1 di output, ma dal tuo disegno ce n'è solo uno.

Il diagramma degli stati comunque non mi torna, in particolare dallo stato 0 con ingresso 1 l'output dovrebbe essere 1, non zero. Che ci sia un errore lo vedi anche contando il numero di uscite pari a 1: nella consegna sono previsti due 1 di output, ma dal tuo disegno ce n'è solo uno.

3

voti

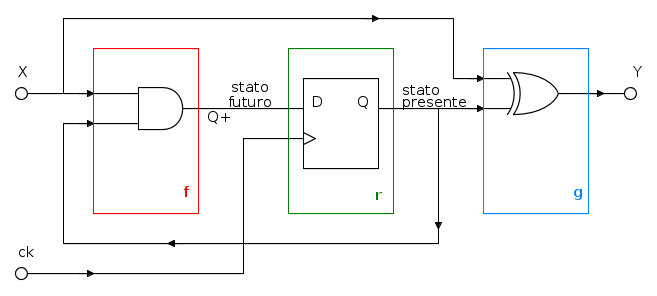

...e per quanto riguarda la sintesi della macchina a stati finiti via FF di tipo D, basta ricordare che (dalla tabella di eccitazione associata allo stesso), il suo ingresso D "copia" semplicemente lo stato futuro.

Ne segue che, dalla semplice ispezione della descrizione iniziale, l'ingresso D del FF sarà ottenibile da una semplice porta AND fra ingresso X e stato Q, e sempre dalla stessa, senza scomodare Karnaugh, è evidente che per ottenere la funzione d'uscita basterà un semplice OR esclusivo fra X e Q.

A dire il vero è un'automa un po' "strano", specie se lo stato iniziale è quello 0, in quanto se partiamo da lì, nello stato 1 non ci si arriverà mai e l'uscita, copiando semplicemente l'ingresso, renderebbe completamente inutile l'uso di una macchina sequenziale, se invece partiamo da stato iniziale 1, la macchina un qualche senso l'avrebbe ... tutto da scoprire.

A mio parere, dare problemi di questo tipo, senza partire dalle specifiche funzionali reali che la FSM deve sintetizzare fa perdere la vera essenza della macchina sequenziale.

Ne segue che, dalla semplice ispezione della descrizione iniziale, l'ingresso D del FF sarà ottenibile da una semplice porta AND fra ingresso X e stato Q, e sempre dalla stessa, senza scomodare Karnaugh, è evidente che per ottenere la funzione d'uscita basterà un semplice OR esclusivo fra X e Q.

A dire il vero è un'automa un po' "strano", specie se lo stato iniziale è quello 0, in quanto se partiamo da lì, nello stato 1 non ci si arriverà mai e l'uscita, copiando semplicemente l'ingresso, renderebbe completamente inutile l'uso di una macchina sequenziale, se invece partiamo da stato iniziale 1, la macchina un qualche senso l'avrebbe ... tutto da scoprire.

A mio parere, dare problemi di questo tipo, senza partire dalle specifiche funzionali reali che la FSM deve sintetizzare fa perdere la vera essenza della macchina sequenziale.

"Il circuito ha sempre ragione" (Luigi Malesani)

1

voti

icaf ha scritto:rende tutto più chiaro...

utilizzando fidocadj oltre che rendere tutto più chiaro si rende tutto più agevole per chi interviene ed anche per te ..

1

voti

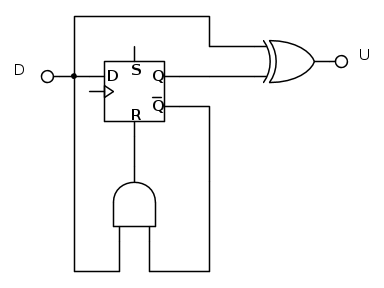

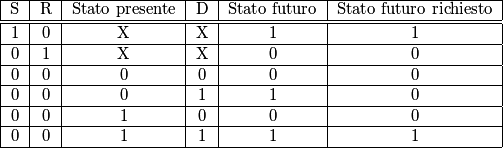

In pratica, considerando la tavola della verità di un D-FLIP FLOP, considerando i segnali di Set (S) e Reset (R) attivi alti, abbiamo:

e cioè che lo "Stato futuro" ricopia lo stato dell'ingrsso D.

Nella tua tabella, invece sinota che in corrispondenza della condizione "Stato presente" a 0 e ingresso D a 1 lo "Stato futuro" è pari a 0.

Per ottenere ciò si dovrà comandare l'ingresso R con un segnale derivato da un AND dell'ingresso D e dell'uscita negata, inoltre, se ho ben interpretato, l'uscita di tutto l'insieme non è altro che un OR ESCLUSIVO tra l'uscita del D-FLIP FLOP e l'ingrsso D.

Max

Max

e cioè che lo "Stato futuro" ricopia lo stato dell'ingrsso D.

Nella tua tabella, invece sinota che in corrispondenza della condizione "Stato presente" a 0 e ingresso D a 1 lo "Stato futuro" è pari a 0.

Per ottenere ciò si dovrà comandare l'ingresso R con un segnale derivato da un AND dell'ingresso D e dell'uscita negata, inoltre, se ho ben interpretato, l'uscita di tutto l'insieme non è altro che un OR ESCLUSIVO tra l'uscita del D-FLIP FLOP e l'ingrsso D.

Max

Max-

Max2433BO

Max2433BO

18,6k 4 11 13 - G.Master EY

- Messaggi: 4724

- Iscritto il: 25 set 2013, 16:29

- Località: Universo - Via Lattea - Sistema Solare - Terzo pianeta...

2

voti

Ciao  RenzoDF

RenzoDF

... infatti sarebbe in contrasto con gli ingressi S (set) e R (Reset) dei RS FLIP FLOP.

Io ho sempre trovato scritto PR (per Preset, al posto di S) e CL (per Clear al posto di R), ma il comonente D FLIP FLOP presente su Fidocadj era disegnato così...

Quindi citando Jessica Rabbit: "(...) no è colpa mia, mi disegnano così!"

Max

Max

... infatti sarebbe in contrasto con gli ingressi S (set) e R (Reset) dei RS FLIP FLOP.

Io ho sempre trovato scritto PR (per Preset, al posto di S) e CL (per Clear al posto di R), ma il comonente D FLIP FLOP presente su Fidocadj era disegnato così...

Quindi citando Jessica Rabbit: "(...) no è colpa mia, mi disegnano così!"

Max

Max-

Max2433BO

Max2433BO

18,6k 4 11 13 - G.Master EY

- Messaggi: 4724

- Iscritto il: 25 set 2013, 16:29

- Località: Universo - Via Lattea - Sistema Solare - Terzo pianeta...

3

voti

Dire che lo schema della FSM secondo Mealy, indicante il blocco logico della "funzione stato futuro f", della "funzione d'uscita g" e "registro di stato r", potrebbe essere il seguente

"Il circuito ha sempre ragione" (Luigi Malesani)

1

voti

All'inizio anch'io avevo pensato ad una soluzione del genere, ma, erroneamente, mi sono detto:

se lo "stato presente" è 0, per quasliasi valore di X, l'uscita Q+ (che è l'ingresso D del FLIP FLOP) sarà sempre pari a 0, quindi come fa l'uscita del FLIP FLOP D a commutare dalla condizione "stato presente" uguale a 0 a "stato futuro" uguale a 1?

Dov'è l'errore del mio ragionamento?

se lo "stato presente" è 0, per quasliasi valore di X, l'uscita Q+ (che è l'ingresso D del FLIP FLOP) sarà sempre pari a 0, quindi come fa l'uscita del FLIP FLOP D a commutare dalla condizione "stato presente" uguale a 0 a "stato futuro" uguale a 1?

Dov'è l'errore del mio ragionamento?

-

Max2433BO

Max2433BO

18,6k 4 11 13 - G.Master EY

- Messaggi: 4724

- Iscritto il: 25 set 2013, 16:29

- Località: Universo - Via Lattea - Sistema Solare - Terzo pianeta...

1

voti

Max2433BO ha scritto:... Dov'è l'errore del mio ragionamento?

Non c'è errore nel tuo ragionamento, se lo stato iniziale Q è lo stato 0 del pallogramma, lo stato futuro Q+ sarà sempre zero ... mi sembrava di aver già commentato il problema in [3].

"Il circuito ha sempre ragione" (Luigi Malesani)

16 messaggi

• Pagina 1 di 2 • 1, 2

Chi c’è in linea

Visitano il forum: Majestic-12 [Bot] e 211 ospiti

Elettrotecnica e non solo (admin)

Elettrotecnica e non solo (admin) Un gatto tra gli elettroni (IsidoroKZ)

Un gatto tra gli elettroni (IsidoroKZ) Esperienza e simulazioni (g.schgor)

Esperienza e simulazioni (g.schgor) Moleskine di un idraulico (RenzoDF)

Moleskine di un idraulico (RenzoDF) Il Blog di ElectroYou (webmaster)

Il Blog di ElectroYou (webmaster) Idee microcontrollate (TardoFreak)

Idee microcontrollate (TardoFreak) PICcoli grandi PICMicro (Paolino)

PICcoli grandi PICMicro (Paolino) Il blog elettrico di carloc (carloc)

Il blog elettrico di carloc (carloc) DirtEYblooog (dirtydeeds)

DirtEYblooog (dirtydeeds) Di tutto... un po' (jordan20)

Di tutto... un po' (jordan20) AK47 (lillo)

AK47 (lillo) Esperienze elettroniche (marco438)

Esperienze elettroniche (marco438) Telecomunicazioni musicali (clavicordo)

Telecomunicazioni musicali (clavicordo) Automazione ed Elettronica (gustavo)

Automazione ed Elettronica (gustavo) Direttive per la sicurezza (ErnestoCappelletti)

Direttive per la sicurezza (ErnestoCappelletti) EYnfo dall'Alaska (mir)

EYnfo dall'Alaska (mir) Apriamo il quadro! (attilio)

Apriamo il quadro! (attilio) H7-25 (asdf)

H7-25 (asdf) Passione Elettrica (massimob)

Passione Elettrica (massimob) Elettroni a spasso (guidob)

Elettroni a spasso (guidob) Bloguerra (guerra)

Bloguerra (guerra)